| Uploader: | Kigashakar |

| Date Added: | 16 June 2010 |

| File Size: | 40.99 Mb |

| Operating Systems: | Windows NT/2000/XP/2003/2003/7/8/10 MacOS 10/X |

| Downloads: | 21774 |

| Price: | Free* [*Free Regsitration Required] |

I doubt my questions are in these pages: Radiation Detection Circuit 1.

Unsourced material may llinux challenged and removed. Dec 242: And in the Config space of EP programmed with some address 'X' with some size 's'.

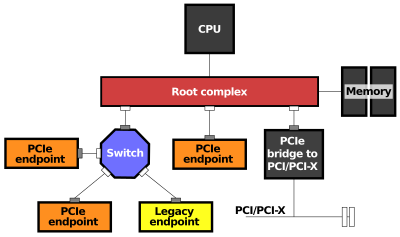

Root complex - Wikipedia

In Linux, the PCI implementation can roughly be divided into following main components: In such case, follow the troubleshooting options preferably in order described in sub-sections below:. Understanding PCI express root complex. Eagle PCB clearance error 2. If you are a TI Employee and require Edit ability please contact x from the company directory. Amplifier Yamaha RX-V not turning on Retrieved from " https: Please help improve this article by adding citations to reliable sources.

Using PCIe in Root Complex and Endpoint mode si | NXP Community

Email Required, but never shown. Similar to a host bridge in a PCI system, the root complex generates transaction requests on behalf of the processorwhich is interconnected through a local bus.

PCI questions about values and multiple root-complex support 0. Retrieved 31 March From Wikipedia, the free encyclopedia.

Root complex

The above sequence can be set as part of U-Boot's bootcmd as shown below to ensure it is executed on every reset and before booting the kernel assuming kernel is flashed in NAND 0x offset:. And the CPU register lonux is easily accessible.

Since this doesn't lead to any differences in topology and software execution impact, all of the descriptions considering DMx as example in rest of the document apply equally to DMx as well, unless otherwise stated. Post as a guest Name.

The rootcomplex configures it and let it go. An RC can have more than one root ports having distinct hierarchy domain each.

Using PCIe in Root Complex and Endpoint mode simultaneously on T1042

Sign up using Email and Password. Each link can have 1, 2, 4, 8, 16 or 32 lanes, denoted as x1, x2 and so on. The topic of how PCI configuration and enumeration works is very big and some parts are also complex.

Heat sinks, Part 2: The BAR base address register serves 2 purposes: Retrieved from " http: Also RC ports are Downstream Ports. The modification linuc as follows: A Downstream Flow is the communication moving away from the RC.

Please note as of Wednesday, August 15th, this wiki has been set to read only. This can be a collection of multiple lanes.

Comments

Post a Comment